Journal of Zhejiang University-SCIENCE C (Computers & Electronics) ISSN 1869-1951 (Print); ISSN 1869-196X (Online) www.zju.edu.cn/jzus; www.springerlink.com E-mail: jzus@zju.edu.cn

# Low temperature Si/Si wafer direct bonding using a plasma activated method\*

Dong-ling LI<sup>†1,2,3</sup>, Zheng-guo SHANG<sup>1,2,3</sup>, Sheng-qiang WANG<sup>1,2,3</sup>, Zhi-yu WEN<sup>1,2,3</sup>

(<sup>1</sup>National Key Laboratory of Fundamental Science of Novel Micro/Nano Device and System Technology, Chongqing University, Chongqing 400044, China)

(<sup>2</sup>MOE Key Laboratory of Optoelectronic Technology & Systems, Chongqing University, Chongqing 400044, China) (<sup>3</sup>Microsystem Research Center, Chongqing University, Chongqing 400044, China)

†E-mail: lidongling@cqu.edu.cn

Received Oct. 8, 2012; Revision accepted Jan. 14, 2013; Crosschecked Mar. 13, 2013

**Abstract:** Manufacturing and integration of micro-electro-mechanical systems (MEMS) devices and integrated circuits (ICs) by wafer bonding often generate problems caused by thermal properties of materials. This paper presents a low temperature wafer direct bonding process assisted by  $O_2$  plasma. Silicon wafers were treated with wet chemical cleaning and subsequently activated by  $O_2$  plasma in the etch element of a sputtering system. Then, two wafers were brought into contact in the bonder followed by annealing in  $N_2$  atmosphere for several hours. An infrared imaging system was used to detect bonding defects and a razor blade test was carried out to determine surface energy. The bonding yield reaches 90%–95% and the achieved surface energy is  $1.76 \text{ J/m}^2$  when the bonded wafers are annealed at  $350 \, ^{\circ}\text{C}$  in  $N_2$  atmosphere for 2 h. Void formation was systematically observed and elimination methods were proposed. The size and density of voids greatly depend on the annealing temperature. Short  $O_2$  plasma treatment for  $60 \, \text{s}$  can alleviate void formation and enhance surface energy. A pulling test reveals that the bonding strength is more than  $11.0 \, \text{MPa}$ . This low temperature wafer direct bonding process provides an efficient and reliable method for 3D integration, system on chip, and MEMS packaging.

**Key words:** Low temperature, Wafer direct bonding, O<sub>2</sub> plasma activation, Surface energy, Void formation **doi:**10.1631/jzus.C12MNT02 **Document code:** A **CLC number:** TN305.7

## 1 Introduction

Wafer bonding has been identified as an enabling technology for the fabrication of micro-electromechanical systems (MEMS) (Huang *et al.*, 2003) and silicon on insulator (SOI) materials (Dunare *et al.*, 2000), and 3D integration (Ko and Chen, 2010). During the last decade, wafer bonding technologies have been developed in two main directions: one is bonding with intermediate layers, such as adhesive bonding using polymer intermediate layers (Seok

et al., 2008), eutectic bonding (Sohn et al., 2007), and metal diffusion bonding (Tsau et al., 2004), and the other is direct bonding using special surface preparation techniques (Lai et al., 2004; Suga et al., 2004; Kowal et al., 2009). Compared to other bonding technology, wafer direct bonding avoids pollution caused by intermediate material and does not need an external electric field, which makes it very attractive in various processes related to MEMS and integrated circuits (ICs) manufacturing.

In conventional wafer direct bonding, a high annealing temperature (800–1100 °C) is essential for a strong bonding interface (Gösele and Tong, 1998). However, such a high temperature hampers the wide applications of wafer direct bonding, since many problems resulting from thermal damage can take place during the annealing steps. Such problems

<sup>\*</sup> Project supported by the Foreign Cultural and Educational Experts Employing Plan, Ministry of Education, China (No. TS2010CQDX 056) and the Fundamental Research Funds for the Central Universities, China (No. CDJZR12135502)

$<sup>\</sup>ensuremath{\mathbb{C}}$  Zhejiang University and Springer-Verlag Berlin Heidelberg 2013

include change in abrupt doping profile, residual stresses of hetero-bonded wafers with different thermal expansion coefficients, degradation of temperature sensitive devices, and damage of low melting point metallic layers and polymers (Kowal *et al.*, 2009; Howlader and Zhang, 2010). To avoid these adverse effects, low temperature wafer bonding technology is strongly desirable.

Many efforts have been made to reduce the annealing temperature. The main mechanism of these methods is based on surface chemical activation resulting in modified chemical bonds at room temperature and requiring less energy during the thermal annealing steps. Two main categories of surface activation processes are used: wet chemical activation, treating pre-bonding wafers with various reagent combinations, such as HNO<sub>3</sub>+H<sub>2</sub>O<sub>2</sub>, H<sub>2</sub>SO<sub>4</sub>+H<sub>2</sub>O<sub>2</sub>, NH<sub>3</sub>·H<sub>2</sub>O+H<sub>2</sub>O<sub>2</sub>+H<sub>2</sub>O (Zhao et al., 2012), and dry activation, such as the plasma activated method (Christiansen et al., 2006; Taniyama et al., 2008) and the ultraviolet (UV) activated method (Lin et al., 2007). It is found that for hydrophilic wafer bonding, the surface energy of wet chemical activations is much lower than that of the O<sub>2</sub> plasma activated method (Pasquariello et al., 2001). Although some researchers have proved that UV exposure can enhance the bonding quality (Lin et al., 2007), the bonding mechanism and process are both immature, which prevents the wide use of this method. Therefore, the plasma activated method becomes a useful method for low temperature wafer direct bonding. Otherwise, to further increase the bonding strength and decrease annealing temperature, some other activation methods based on plasma activated bonding (PAB) have been employed, such as the PAB with a nanoadhesion layer (Kondou et al., 2012) and the sequential plasma activated bonding (SPAB) (Suga et al., 2004; Wang et al., 2007). However, these processes highly depend on plasma activated equipments, and are usually followed by a complex activation process or a long time annealing. Furthermore, voids usually occur after low temperature annealing processes with no exception in wafer direct bonding, which is quite harmful for the subsequent process and device reliability (Zhang and Raskin, 2005).

This work focuses on developing a simple Si/Si bonding process that enables a high bonding quality at low temperature. The O<sub>2</sub> plasma activated method is

employed. The annealing temperature is as low as 350 °C and the whole process is achieved within 3 h. The bonding quality is evaluated by an infrared (IR) imaging system, razor blade test, and tensile pulling test. The surface energy vs. various process parameters is characterized. The void formation features at different annealing temperatures have been studied and an elimination method is proposed.

#### 2 Hydrophilic wafer direct bonding

In this paper, only the hydrophilic wafer bonding is considered, since its surface energy is much greater than that of the hydrophobic bonding when the annealing temperature is below 500 °C (Christiansen *et al.*, 2006). Upon cleaning the silicon wafers with strongly oxidizing solutions or plasma, the surfaces are full of the silanol group (Si-OH). At room temperature (25±2 °C), the bonding phenomenon seems to be entirely based on weak van der Waals forces and adhere through hydrogen bridge bonds. The bonding energy at this point is weak and is in the order of 0.1 J/m² (Reiche, 2006). By the subsequent annealing step, strong Si–O–Si bonds are formed, as illustrated by

$$Si - OH + OH - Si \rightarrow Si - O - Si + H_2O.$$

(1)

This reaction may occur at temperatures as low as about 100 °C. A small part of the removal of water molecules may occur by lateral diffusion along the bonding interface to the rim of the wafers, but most water molecules diffuse through the native oxide to the bulk silicon where they react to form silicon dioxide and hydrogen:

$$Si + H_2O \rightarrow SiO_2 + H_2.$$

(2)

This reaction ends at a few hundred degrees, which leads to the plateau. The remaining increase of the surface energy is associated with micro-gaps at the interface in which nitrogen may possibly remain trapped and may be eliminated by viscous flow of the oxide at high temperatures. Alternatively, bonding in vacuum, which prevents the trapping of inert gas, and long annealing (e.g., 100 h) at low temperatures, may also lead to the full surface energy and a bonding

equivalent to that achieved after conventional annealing at 1100 °C (Schmidt, 1998).

### 3 Experiments

Commercially available silicon wafers, 100 mm in diameter and 525-µm thick, were used in this study. They were n-type, (100)-oriented, one side polished, Czochralsky (CZ)-grown bare wafers. The wafers were first cleaned in the standard clean 1 (SC1,  $NH_3 \cdot H_2O : H_2O_2 : H_2O = 1:1:5$  (volume ratio), 80 °C for 10 min) and standard clean 2 (SC2, HCl:H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O=1:1:5 (volume ratio), 80 °C for 10 min) solutions, and then rinsed in deionization (DI) water. For rendering the bonding surfaces highly hydrophilic and particles free, the wafers were then cleaned in RCA1 once more. Thereafter, both wafers were activated in the etch unit of sputtering system FHR MS100×6-L, with the O<sub>2</sub> flow of 50 standard-state cubic centimeters per min (sccm), chamber pressure of 2.5 Pa, DC bias of 383 V, radio frequency (RF) power of 50 W, and the exposure time varying from 60 to 300 s. For further cleaning and being highly hydrophilic, the silicon wafers were then rinsed in megasonic cleaning system M4L for 15 min.

Prebonding was conducted automatically in the bonder Suss SB6e at room temperature right after surface pretreatment. The chamber pressure was  $5\times10^{-3}$  Pa, and the tool pressure was  $3\times10^{5}$  Pa (7000 N). For further increase of surface energy, the bonded wafers were annealed in  $N_2$  atmosphere for about 2 to 10 h. Annealing temperatures were chosen from 200–1000 °C.

All of the bonded wafer pairs were inspected by an IR imaging system before and after annealing. The bonding quality was evaluated by razor blade test and tensile pulling test. The cross section of the bonding interface was observed by a scanning electron microscope (SEM).

### 4 Results and discussion

## 4.1 Yield

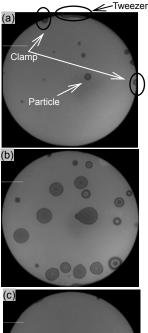

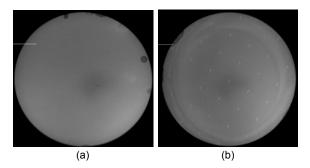

Yield and reproducibility are crucial properties for wafer bonding. In our experiments, different parameters resulting in unsuccessful bonding are studied. Generally, non-bonded areas (dark fields) concentrate on the wafer rim (Fig. 1a). It is caused mainly by handling with tweezers or mechanical clamping in the SB6e. Some non-bonded areas appear in the center of the bonded wafers right after prebonding at room temperature, which is due to particles brought by the wet chemical cleaning or the plasma activated process. Particles on the surface have the most severe influence on wafer direct bonding. They act as spacers and produce a separation. A 1-µm large particle on a silicon wafer (100 mm in diameter) produces a void of about 1 cm in diameter (Plößl and Kräuter, 1999), which significantly influences the bonding yield. Fig. 1b shows the defects caused by the organic contaminant. This kind of defect does not occur or at least is not large enough to be detected by the IR imaging system, but then during the thermal annealing step, the decomposition of the organic contaminant occurs and big voids appear. It turns out that the surface pretreatment is the critical parameter concerning the bonding yield. By strictly following the wet chemical cleaning procedure and optimizing plasma activated parameters, the entire area is strongly bonded except for some regions around the circumference. The bond yield reaches 90%-95% (Fig. 1c).

Fig. 1 Infrared (IR) images of Si/Si wafer direct bonding with different kinds of defects

(a) After prebonding, defects caused by particles, clamps, and tweezers occur; (b) After annealing, voids caused by an organic contaminant occur; (c) Optimized wafer bonding. Dark fields show non-bonded areas

#### 4.2 Surface energy

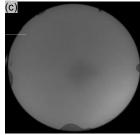

The razor blade test is the most convenient method to determine the surface energy for Si/Si bonding wafers. A thin razor blade is inserted into the bonded pairs from the edges (Fig. 2), and the crack propagation length is observed by an IR imaging system (Fig. 3).

Fig. 2 Schematic diagram of razor blade test

Fig. 3 Infrared (IR) image of the crack opening

The surface energy  $\gamma$  can be calculated as

$$\gamma = \frac{3}{32} \cdot \frac{Et_{\rm w}^3 t_{\rm b}^2}{a^4},\tag{3}$$

where E is Young's modulus,  $t_b$  is the blade thickness,  $t_w$  is the wafer thickness, and a is the crack propagation length.

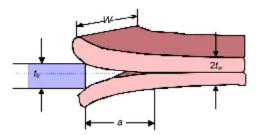

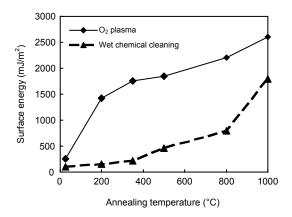

Surface energy vs. various process parameters has been measured to study the evolution of surface energy. Fig. 4 illustrates a plot of the surface energy vs. annealing time for wafers activated by the  $\rm O_2$  plasma and the wet chemical cleaning. It is observed that the surface energy at room temperature is  $\rm 0.26~J/m^2$  for bonded wafers activated by the  $\rm O_2$  plasma compared to 0.1 J/m² for bonded wafers treated with the chemical cleaning. After 2 h of annealing at 350 °C, the surface energy reaches  $\rm 1.76~J/m^2$  for bonded wafers activated by the  $\rm O_2$  plasma, which is nearly three times higher than that

for bonded wafers treated with the wet chemical cleaning. It is concluded that the O<sub>2</sub> plasma activated method results in a higher surface energy. During the O<sub>2</sub> plasma activation process, the surface chemical bonds of silicon wafers will be broken, and then absorb plenty of water to form Si-OH (Eichler *et al.*, 2008). Therefore, the quantity of Si-O-Si bonds increases and the surface energy becomes higher. In addition, the surface energy increases rapidly with the increase of annealing time. However, when the annealing time exceeds 2 h, the surface energy increases slightly and almost remains the same. After 2-h annealing, the bonding process reaches a saturation state, and all of the hydrogen bonds have been transformed into Si-O-Si bonds.

Fig. 4 Surface energy vs. annealing time (annealed at 350  $^{\circ}\text{C})$

Fig. 5 shows the surface energy as the function of annealing temperature. For 2 h annealing time, the surface energy increases drastically from room temperature to 350 °C, and keeps a slight increase afterwards until the annealing temperature is higher than 500 °C. This can be explained by the bonding mechanism at different temperatures. From room temperature to 100 °C, the bonded wafers are combined by hydrogen bond, and the surface energy is weak. With the increase of annealing temperature, the migration rate of OH groups increases, consequently accelerating the bonding process and increasing the surface energy rapidly. Meanwhile, the hydrogen bond is replaced by the Si-O-Si bond, and this reaction is finished at about 350 °C. For further increase of annealing temperature, the Si-O-Si bonds are destroyed by OH, and then the Si-O bonds are formed. Furthermore, the high temperature will cause slight deformation of the silicon wafers, and the bonded pairs can be combined more tightly.

Fig. 5 Surface energy vs. annealing temperature of bonded wafers (annealed for 2 h)

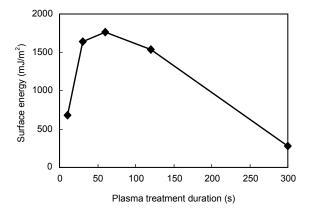

Plasma treatment durations have also been studied (Fig. 6). It is observed that the surface energy after the  $O_2$  plasma activation initially rises strongly with the increase of treatment time and reaches a maximum value at about  $1.76 \text{ J/m}^2$  beyond t=60 s. Then, the surface energy exhibits a declining tendency. Since insufficient treatment time of the  $O_2$  plasma not only provides insufficient dangling bonds for wafer bonding, but organic contaminants can also not be completely removed, the surface energy is low. As a contrast, excessive  $O_2$  plasma treatment will increase the surface roughness, which also reduces the surface energy.

Fig. 6 Surface energy vs. plasma treatment time (annealed at 350  $^{\circ}\mathrm{C})$

### 4.3 Bonding strength

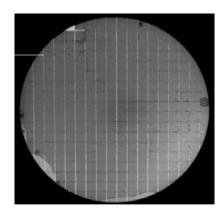

A tensile pulling test was performed to determine the bonding strength. The bonded wafers were diced into 5 mm×5 mm pieces. The dicing process is so perfect that no cleavages are formed in the bonding area (Fig. 7). The white areas at the edges of the bonded wafers are due to the razor blade test. It implies that the bonding strength is sufficient to withstand subsequent manufacturing processes.

Fig. 7 Infrared (IR) image of the bonded wafer diced into 5 mm×5 mm pieces

The small pieces were glued on metal bars with epoxy resin (Fig. 8). To obtain strong adhesion, the samples were placed at room temperature for 24 h and baked at 60 °C for 2 h.

Fig. 8 Specimen for the pulling test

The bonding strengths for various samples were tested, as shown in Table 1. It reveals that the  $\rm O_2$  plasma activated for 60 s displays the best bonding strength. The samples are all fractured from the glue area and the bonding strength is more than 11.0 MPa. When prolonging plasma treatment duration to 120 s, the bonding strength decreases to about 8.2 MPa. The reason is estimated to be the increase of the surface roughness and bonding voids due to the surplus reaction. Samples only treated with the wet chemical cleaning acquire bonding strength of 2.4 MPa. It can also be concluded that  $\rm O_2$  plasma activation significantly increases the bonding quality.

Table 1 Bonding strengths of various samples

| Sample treatment                        | Average load (N) | Bonding<br>strength (MPa) |

|-----------------------------------------|------------------|---------------------------|

| Wet chemical cleaning                   | 61               | 2.4                       |

| O <sub>2</sub> plasma treated for 60 s  | 270              | 11.0                      |

| O <sub>2</sub> plasma treated for 120 s | 207              | 8.2                       |

To inspect the bonding interface more closely, the cross sections of small pieces were scanned by SEM (Fig. 9). The interfacial material is found to impenetrate into each other, thus forming high bonds across the interface. The interface is so thin that it is difficult to measure the thickness by SEM. It indicates that the two wafers are combined tightly and no voids occur. Some research reported that wafer bonding of hydrophilic surfaces results in the presence of an oxide layer in the interface, and the thickness is only a few nanometers (Gösele and Tong, 1998; Plach *et al.*, 2012). Therefore, the properties of the interface must be further studied and deep research of the bonding interface must be done in our later work.

Fig. 9 Scanning electron microscope (SEM) of the Si/Si bonding interface

## 4.4 Void formation

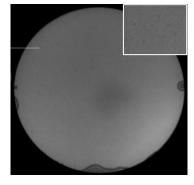

In hydrophilic wafer direct bonding, interfacial voids inevitably occur after low temperature annealing. The main origins of interfacial voids have been classified in two forms: thermal voids caused by thermal decomposition of surface contaminants like hydrocarbons, and intrinsic voids generated by the oxidation reaction of interface water with silicon at

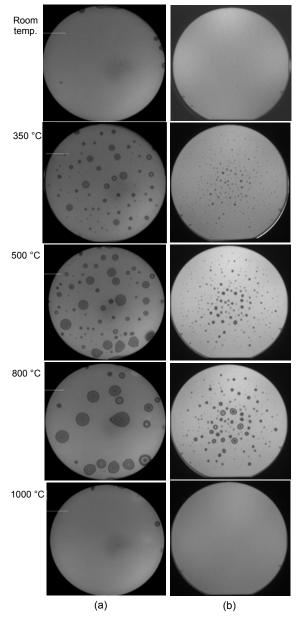

higher temperature or caused by hydrogen desorbed from hydrides (Zhang and Raskin, 2005). Different annealing temperatures from 350 to 1000 °C were applied not to increase the bonding strength but to study the void formation. IR images of Si/Si bonded wafers treated by the wet chemical cleaning method and the O<sub>2</sub> plasma activated method are demonstrated in Figs. 10a and 10b, respectively. It is clearly shown that the size and density of voids depend strongly on the annealing temperature. Taking bonded wafers treated with O<sub>2</sub> plasma as an example, the maximum void diameter is about 2 mm when the annealing temperature is 350 °C instead of 10 mm after increasing the annealing temperature to 800 °C. The increase of the void size is related to the delamination of the bonded area surface surrounding the void under the pressure generated by trapped gases during annealing. The decrease of the number of voids can be explained by the merging of growing voids that are close enough to each other and the diffusion of gases along the interface. When the annealing temperature exceeds 1000 °C, the gases can be absorbed by the surrounding oxide layer or silicon, and the voids vanish.

Comparing Figs .10a and 10b, it is observed that the void size of the O<sub>2</sub> plasma activation bonded wafers is much smaller than that of the wet chemical cleaning bonded wafers. Further razor blade tests show that the surface energy is much higher. It is concluded that the O<sub>2</sub> plasma process not only removes the organic contaminants from the wafer surface, but also increases the surface energy. However, different from wet chemical cleaning wafer bonding, the void density is much larger and it does not decrease with the increase of annealing temperature as in the case of the O<sub>2</sub> plasma activated wafer bonding. On the one hand, after O<sub>2</sub> plasma activation the hydrophilic degree is well increased thanks to the great number of silanol groups at the wafer surface. This large number of bonding sites generates a great quantity of byproducts such as water and hydrogen. These byproducts will pile and inflate after annealing at low temperatures, resulting in an increased number of interfacial voids. On the other hand, the bonding strength in the case of bonded wafers activated by the O<sub>2</sub> plasma reaches such a high value that the byproducts between the bonding interface cannot diffuse easily along the interface.

Fig. 10 Infrared (IR) images of Si/Si bonded wafers at different annealing temperatures

(a) Wet chemical cleaning; (b) O<sub>2</sub> plasma

The interfacial voids can be avoided by adding an oxide layer between the bonded wafers, as illustrated in Fig. 11a. The oxide layer at the bonding interface can act as an absorbing layer of reaction products and contaminants, reducing the formation of voids. Bonding with patterned wafers can also mitigate interfacial voids. During bonding, the reaction product can be gathered in the 'holes', resulting in no voids bonding at the bonded areas (Fig. 11b). Optimized  $O_2$  plasma activation parameters will also alleviate voids. Comparing Figs. 10b and 12, it is observed that by decreasing the  $O_2$  plasma activation time from 120 to 60 s, the void size decreases dramatically since excessive  $O_2$  plasma causes an excess of chemical reaction byproduct, which results in void formation.

Fig. 11 Infrared (IR) images of void free Si/Si wafer bonding with an oxide layer (a) and patterned wafers (b) annealed at 350  $^{\circ}$ C

Fig. 12 Infrared (IR) image of bonded wafers annealed at 350 °C and O<sub>2</sub> plasma activated for 60 s

## 5 Conclusions

Low temperature Si/Si wafer bonding has been performed by the O<sub>2</sub> plasma activated method. By optimizing the bonding process, the bond yield reaches 90%–95%. The surface energy dependency on annealing temperature and time has been studied to acquire an optimized annealing process. It is shown that the surface energy achieved is 1.76 J/m<sup>2</sup> when the bonded wafer is annealed at 350 °C in N<sub>2</sub> atmosphere for 2 h. The bonded wafers can withstand a dicing experiment. Subsequent pulling tests reveal that the bonding strength is more than 11.0 MPa. Interfacial voids occur after low temperature annealing. The size

and density of voids highly depend on annealing temperature. Compared to bonded wafers treated with wet chemical cleaning, an optimized O<sub>2</sub> plasma activated method can greatly decrease the size of interfacial voids and enhance surface energy. Consequently, the O<sub>2</sub> plasma treatment duration is set to be 60 s with O<sub>2</sub> flow of 55 sccm, chamber pressure of 2.5 Pa, DC bias of 383 V, and RF power of 50 W. It can be assumed that the O<sub>2</sub> plasma activated bonding process is very suitable for high surface energy, low temperature wafer bonding as needed for SOI, MEMS, and wafer scale packaging.

#### References

- Christiansen, S.H., Singh, R., Gösele, U., 2006. Wafer direct bonding: from advanced substrate engineering to future applications in micro/nanoelectronics. *Proc. IEEE*, **94**(12):2060-2106. [doi:10.1109/JPROC.2006.886026]

- Dunare, C., Cernica, I., Popescu, D., Popescu, A., Cristea, D., Modreanu, M., Manea, E., 2000. SOI Materials for MOEMS Obtained by Silicon Direct Bondig Technique. Proc. Int. Semiconductor Conf., p.531-534.

- Eichler, M., Michel, B., Thomas, M., Gabriel, M., Klages, C.P., 2008. Atmospheric-pressure plasma pretreatment for direct bonding of silicon wafers at low temperatures. *Surf. Coat. Technol.*, 203(5-7):826-829. [doi:10.1016/j.surfcoat. 2008.06.054]

- Gösele, U., Tong, Q.Y., 1998. Semiconductor wafer bonding. *Ann. Rev. Mater. Sci.*, **28**(1):215-241. [doi:10.1146/annurev.matsci.28.1.215]

- Howlader, M.M.R., Zhang, F., 2010. Void-free strong bonding of surface activated silicon wafers from room temperature to annealing at 600 °C. *Thin Sol. Films*, **519**(2):804-808. [doi:10.1016/j.tsf.2010.08.144]

- Huang, Y., Ergun, A.S., Hæggström, E., Badi, M.H., Khuri-Yakub, B.T., 2003. Fabricating capacitive micromachined ultrasonic transducers with wafer-bonding technology. *J. Microelectromech. Syst.*, 12(2):128-137. [doi:10.1109/JMEMS.2003.809968]

- Ko, C.T., Chen, K.N., 2010. Wafer-level bonding/stacking technology for 3D integration. *Microelectron. Rel.*, 50(4): 481-488. [doi:10.1016/j.microrel.2009.09.015]

- Kondou, R., Wang, C.X., Shigetou, A., Suga, T., 2012. Nanoadhesion layer for enhanced Si-Si and Si-SiN wafer bonding. *Microelectron. Rel.*, 52(2):342-346. [doi:10. 1016/j.microrel.2010.12.006]

- Kowal, J., Nixon, T., Aitken, N., 2009. Surface activation for low temperature wafer fusion bonding by radicals produced in an oxygen discharge. *Sens. Actuat. A*, 155(1):145-151. [doi:10.1016/j.sna.2009.08.018]

- Lai, S.I., Lin, H.Y., Hu, C.T., 2004. Effect of surface treatment on wafer direct bonding process. *Mater. Chem. Phys.*, **83**(2-3):265-272. [doi:10.1016/j.matchemphys.2003.09. 024]

- Lin, X.H., Shi, T.L., Liao, G.L., Tang, Z.R., Liu, S.Y., Nie, L., 2007. UV Enhanced Low Temperature Wafer Direct Bonding and Interface Quality Test. Proc. 7th IEEE Int. Conf. on Nanotechnology, p.754-758. [doi:10.1109/NANO.2007.4601296]

- Pasquariello, D., Camacho, M., Hjort, K., Dózsa, L., Szentpáli, B., 2001. Evaluation of InP-to-silicon heterobonding. *Mater. Sci. Eng. B*, 80(1-3):134-137. [doi:10.1016/S0921-5107(00)00626-7]

- Plach, T., Hingerl, K., Dragoi, V., Wimplinger, M., 2012. Low

Temperature Plasma Activated Direct Wafer Bonding.

3rd IEEE Int. Workshop on Low Temperature Bonding

for 3D Integration, p.145. [doi:10.1109/LTB-3D.2012.

62380721

- Plößl, A., Kräuter, G., 1999. Wafer direct bonding: tailoring adhesion between brittle materials. *Mater. Sci. Eng. R*, **25**(1-2):1-88. [doi:10.1016/S0927-796X(98)00017-5]

- Reiche, M., 2006. Semiconductor wafer bonding. *Phys. Stat. Sol. A*, **203**(4):747-759. [doi:10.1002/pssa.200564509]

- Schmidt, M.A., 1998. Wafer-to-wafer bonding for microstructure formation. *Proc. IEEE*, **86**(8):1575-1585. [doi:10.1109/5.704262]

- Seok, S., Rolland, N., Rolland, P.A., 2008. A novel packaging method using wafer-level BCB polymer bonding and glass wet-etching for RF applications. *Sens. Actuat. A*, **147**(2):677-682. [doi:10.1016/j.sna.2008.06.008]

- Sohn, Y.C., Wang, Q., Ham, S.J., Jeong, B.G., Jung, K.D., Choi, M.S., Kim, W.B., Moon, C.Y., 2007. Wafer-Level Low Temperature Bonding with Au-In System. Proc. 57th Electronic Components and Technology Conf., p.633-637. [doi:10.1109/ECTC.2007.373863]

- Suga, T., Kim, T.H., Howlader, M.M.R., 2004. Combined Process for Wafer Direct Bonding by Means of the Surface Activation Method. Proc. 54th Electronic Components and Technology Conf., p.484-490.

- Taniyama, S., Wang, Y.H., Fujino, M., Suga, T., 2008. Room Temperature Wafer Bonding Using Surface Activated Bonding Method. IEEE 9th VLSI Packaging Workshop in Japan, p.141-144. [doi:10.1109/VPWJ.2008.4762236]

- Tsau, C.H., Spearing, S.M., Schmidt, M.A., 2004. Wafer-level thermocompression bonds. *J. Microelectromech. Syst.*, **13**(6):963-971. [doi:10.1109/JMEMS.2004.838393]

- Wang, C.X., Higurashi, E., Suga, T., 2007. Room Temperature Si/Si Wafer Direct Bonding in Air. 8th Int. Conf. on Electronic Packaging Technology, p.1-6. [doi:10.1109/ICEPT.2007.4441488]

- Zhang, X.X., Raskin, J.P., 2005. Low-temperature wafer bonding: a study of void formation and influence on bonding strength. *J. Microelectromech. Syst.*, **14**(2): 368-382. [doi:10.1109/JMEMS.2004.839027]

- Zhao, Y.L., Song, Z.J., Li, Y., 2012. Low Temperature Wafer Direct Bonding Using Wet Chemical Treatment. 3rd Int. Conf. on Manufacturing Science and Engineering, p.2381-2384. [doi:10.4028/www.scientific.net/AMR.482-484.2381]