Frontiers of Information Technology & Electronic Engineering www.zju.edu.cn/jzus; engineering.cae.cn; www.springerlink.com ISSN 2095-9184 (print); ISSN 2095-9230 (online) E-mail: jzus@zju.edu.cn

# Design and analysis of carbon nanotube FET based quaternary full adders

Mohammad Hossein MOAIYERI<sup>†‡1,2</sup>, Shima SEDIGHIANI<sup>2</sup>, Fazel SHARIFI<sup>2</sup>, Keivan NAVI<sup>2</sup>

(¹Faculty of Electrical Engineering, Shahid Beheshti University, Tehran 1983963113, Iran) (²Nanotechnology and Quantum Computing Lab, Shahid Beheshti University, Tehran 1983963113, Iran) †E-mail: h\_moaiyeri@sbu.ac.ir

Received July 7, 2015; Revision accepted Sept. 24, 2015; Crosschecked Sept. 20, 2016

**Abstract:** CMOS binary logic is limited by short channel effects, power density, and interconnection restrictions. The effective solution is non-silicon multiple-valued logic (MVL) computing. This study presents two high-performance quaternary full adder cells based on carbon nanotube field effect transistors (CNTFETs). The proposed designs use the unique properties of CNTFETs such as achieving a desired threshold voltage by adjusting the carbon nanotube diameters and having the same mobility as p-type and n-type devices. The proposed circuits were simulated under various test conditions using the Synopsys HSPICE simulator with the 32 nm Stanford comprehensive CNTFET model. The proposed designs have on average 32% lower delay, 68% average power, 83% energy consumption, and 77% static power compared to current state-of-the-art quaternary full adders. Simulation results indicated that the proposed designs are robust against process, voltage, and temperature variations, and are noise tolerant.

**Key words:** Nanoelectronics, Carbon nanotube FET, Multiple-valued logic, Quaternary logic http://dx.doi.org/10.1631/FITEE.1500214 **CLC number:** TN79

#### 1 Introduction

Technology dimension scaling, which increases the chip density and the number of economic circuits, is significant due to the widespread use of wireless communication and portable computing systems. Power density, design complexity, fabrication costs, and robustness are the important concerns for digital circuits and systems design. By the continuous scaling down of the feature size, interconnection has become the dominant component of delay, area, and power consumption in modern chips. Therefore, to overcome these problems and limitations, finding a new computing method seems to be a necessity.

The use of multiple-valued logic (MVL) can be an ultimate and suitable solution to solve the limitaAlthough ternary logic (radix-3) has been proved to be the most efficient MVL system (Hurst, 1984), quaternary logic has the advantage of easier communication with binary logic circuits and consequently less complex radix conversions.

The development of nanoelectronics has introduced new materials and devices with many key properties which can help researchers to overcome physical limitations and challenges caused by MOSFET scaling (Mansoori and Soelaiman, 2005). Considering the nanodevices introduced so far,

tions of scaling. First, more data can be transferred by MVL in wired communication and consequently a dramatic reduction in chip area, complexity, and power consumption of wires can be achieved. In addition, serial-parallel arithmetic operation can be carried out faster (Hurst, 1984; Dubrova, 1999; Navi et al., 2011). Thereby, lower chip complexity, increased computational ability, higher performance and reduced interconnect congestion motivate the use of MVL in a wide variety of applications.

<sup>&</sup>lt;sup>‡</sup> Corresponding author

<sup>©</sup> ORCID: Mohammad Hossein MOAIYERI, http://orcid.org/0000-0001-9711-7923

<sup>©</sup> Zhejiang University and Springer-Verlag Berlin Heidelberg 2016

carbon nanotube field effect transistors (CNTFETs) are most likely to succeed in replacing MOSFET in future because of their electrical behavior and physical structure. Their very high carrier mobility, considerably higher carrier saturation velocity, near ballistic carrier transport, equal mobility for electrons and holes, very low OFF-current, and easy integration with high-k insulation materials give CNTFETs great potential for improving the performance of integrated circuits. More importantly, the desired CNTFET threshold voltage can be achieved by adjusting the diameter of the CNTs (Liang et al., 2014). Many feasible and effective strategies have already been published for growing CNTs with a specified chirality and adopting the desired threshold voltage for multitube CNTFETs (Chen et al., 2007; Lin et al., 2009; Yang et al., 2014).

Three types of CNTFETs have been introduced, SB-CNTFET, T-CNTFET, and MOSFET-like CNTFET. Of these, MOSFET-like CNTFET behaves like a normal MOSFET and demonstrates unipolar characteristics. Furthermore, it is suitable for ultra-high-performance CMOS-like designs because of its high  $I_{\rm ON}/I_{\rm OFF}$  ratio (Raychowdhury and Roy, 2007). In this study, MOSFET-like CNTFETs were used for the design and simulation of all circuits.

MVL circuit designs based on CNTFET have attracted attention in recent years and many CNT-FET-based binary and ternary logic and arithmetic circuits have been proposed (Raychowdhury and Roy, 2005; Lin et al., 2011; Moaiyeri et al., 2011; Liang et al., 2014). However, less effort has been put into developing quaternary full adders due to a lack of efficient circuit models and design challenges, especially for those based on MOSFET. Previous MOSFET-based quaternary full adders were designed using depletion-mode devices, which are not applicable to recent nanoscale FET technologies (Thoidis et al., 1998; Datla et al., 2009). The adder is undoubtedly the most important circuit among the various processing elements used in a microprocessor. Performance improvement of signal processors depends mainly on the development of adder circuits. Therefore, designing an efficient CNTFET-based quaternary full adder cell supporting all the possible logic values for near future non-silicon non-binary integrated circuits and systems is of considerable interest.

This paper presents two quaternary full adders using CNTFET as an emerging nanotechnology. Since the proposed quaternary cells functionality supports all the possible quaternary logics for all three inputs, they can also be referred to as quaternary 3-to-2 compressor circuits (Datla, 2009). There is no need for radix conversions to perform quaternary arithmetic operations in the proposed designs, which makes these designs more efficient than previous systems.

#### 2 Review of quaternary logic design

MVL circuits can be designed by increasing the domain of binary algebra form  $\{0, 1\}$  to  $\{0, 1, ..., M-1\}$ , M>2. For quaternary logic, M is 4 with domain  $D \in \{0, 1, 2, 3\}$ , and the high to low logic voltage level is divided into four levels, which can be considered around 0 V,  $1/3V_{\rm DD}$ ,  $2/3V_{\rm DD}$ , and  $V_{\rm DD}$ . The quaternary AND, OR, and NOT operations are the three most significant operations for implementing other quaternary logic functions. These basic functions can be defined as follows:

$$a \cdot b = \min(a, b),$$

(1)

$$a+b=\max(a,b), \tag{2}$$

$$NOT(a)=3-a. (3)$$

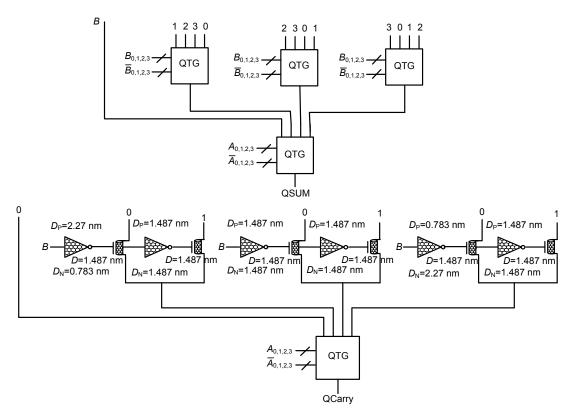

Since half adders (HAs) and full adders (FAs) are considered as the basic elements in almost all arithmetic circuits, optimized MVL half adders and full adders can significantly improve the performance of MVL processing units. A half adder was proposed by Moaiyeri (2012) (Fig. 1). High-performance operation in the presence of process variations has been reported for this design. This design method is based on a quaternary four-to-one multiplexer (MUX) which uses a quaternary decoder and CNTFET-based transmission switches (QTG) as building blocks, and is described in detail by Moaiyeri (2012). The design of the sub-circuits presented by Moaiyeri (2012) was based on transmission switches, pass transistors and threshold detectors.

Based on Eqs. (1) and (2) and a quaternary full adder with A, B,  $C_{in}$  inputs, Eqs. (4) and (5) for quaternary Sum and  $C_{out}$  outputs can be derived, where  $X_0$ ,  $X_1$ ,  $X_2$ , and  $X_3$  binary signals are high, when X is equal to 0, 1, 2, and 3, respectively:

Fig. 1 The quaternary half adder presented by Moaiyeri et al. (2012)

$$\begin{aligned} & \text{SUM} = 1.(C_{\text{in}0}A_0B_1 + C_{\text{in}0}A_0B_1 + C_{\text{in}0}A_2B_3 + C_{\text{in}1}A_0B_0 + C_{\text{in}1}A_1B_3 + C_{\text{in}1}A_3B_1 + C_{\text{in}1}A_2B_2 \\ & + C_{\text{in}2}A_0B_3 + C_{\text{in}2}A_1B_2 + C_{\text{in}2}A_2B_1 + C_{\text{in}2}A_3B_0 + C_{\text{in}3}A_0B_2 + C_{\text{in}3}A_1B_1 + C_{\text{in}3}A_2B_0 + C_{\text{in}3}A_3B_3) \\ & + 2.(C_{\text{in}0}A_0B_2 + C_{\text{in}0}A_1B_1 + C_{\text{in}0}A_2B_0 + C_{\text{in}0}A_3B_3 + C_{\text{in}1}A_0B_1 + C_{\text{in}1}A_1B_0 + C_{\text{in}1}A_2B_3 + C_{\text{in}1}A_3B_2 \\ & + C_{\text{in}2}A_0B_0 + C_{\text{in}2}A_1B_3 + C_{\text{in}2}A_2B_2 + C_{\text{in}2}A_3B_1 + C_{\text{in}3}A_0B_3 + C_{\text{in}3}A_1B_2 + C_{\text{in}3}A_2B_1 + C_{\text{in}3}A_3B_0) \\ & + 3.(C_{\text{in}0}A_0B_3 + C_{\text{in}0}A_1B_2 + C_{\text{in}0}A_2B_1 + C_{\text{in}0}A_3B_0 + C_{\text{in}1}A_0B_2 + C_{\text{in}1}A_1B_1 + C_{\text{in}1}A_2B_0 + C_{\text{in}1}A_3B_3 \\ & + C_{\text{in}2}A_0B_1 + C_{\text{in}2}A_1B_0 + C_{\text{in}2}A_2B_3 + C_{\text{in}0}A_3B_2 + C_{\text{in}3}A_0B_0 + C_{\text{in}3}A_1B_3 + C_{\text{in}3}A_3B_1), \end{aligned} \end{aligned} \tag{4}$$

A method for designing quaternary adders was presented by da Silva *et al.* (2006) based on down literal and successor circuits and transmission gate networks. This circuit was designed specifically for quaternary logic computations.

A quaternary adder was introduced by Sharifi et al. (2015) based on efficient quaternary-to-binary and binary-to-quaternary radix converters. The

addition in this design is performed by means of a transmission gate based (3, 3, 4) compressor.

A radix-4 full adder was presented by Asif and Vesterbacka (2012). This design uses only two states for the input carry digit (0 and 1), which makes it unsuitable for being used as a building block of larger quaternary adders. In addition, to perform quaternary arithmetic operations with a radix-4 FA block, input

quaternary signals (quaternary input signals) should be converted to binary signal. Moreover, converting binary output signals of a radix-4 full adder to quaternary signals is needed. To achieve a complete quaternary full adder in which input and output signals are all quaternary, we modified the radix-4 FA using a binary-to-quaternary conversion before addition and a quaternary-to-binary conversion after addition (Patel and Gurumurthy, 2010).

The two designs last mentioned are inherently binary, which reduces the advantages of MVL and imposes high delay and power overheads.

#### 3 Proposed quaternary full adders

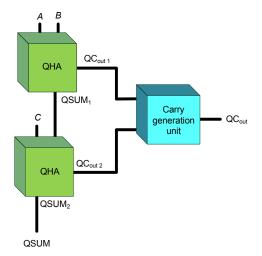

Although a gate-level method like the one proposed by Lin *et al.* (2011) for ternary logic can be used for designing a quaternary adder circuit, it is not an efficient approach because of increasing critical path length and considerable circuit overhead. However, a quaternary full adder can be built by cascading two half adders to add three quaternary inputs A, B, and C, and generate a quaternary sum and a quaternary output carry ( $QC_{out}$ ) as shown in Fig. 2.

Fig. 2 The block diagram of the proposed quaternary full adder

This means that quaternary full addition can be fragmented into quaternary half addition and carry generation operations. By designing the quaternary half adder according to Moaiyeri *et al.* (2012) and the content of Table 1, two novel quaternary full adders are proposed.

Table 1 Deriving final carry based on the partial carries

| QC <sub>out 1</sub> | QC <sub>out 2</sub> | QC <sub>out</sub> |

|---------------------|---------------------|-------------------|

| 0                   | 0                   | 0                 |

| 0                   | 1                   | 1                 |

| 1                   | 0                   | 1                 |

| 1                   | 1                   | 2                 |

The context of Table 1 shows that QC<sub>out</sub> at the output of the carry generation unit may have '0', '1', and '2' logic values equivalent to 0, 0.3, and 0.6 V voltage levels, respectively. It means a ternary module can be used instead of a quaternary one for the carry generation unit, which leads to a saving in the number of transistors. The next two subsections present two different designs for the carry generation unit.

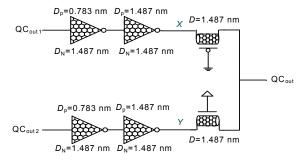

#### 3.1 The first proposed carry generation unit

Based on Table 1 and the complementary CNTFET-based design method, the first proposed idea has a structure based on two CNTFET binary inverters with a 0.6 V power supply, which are cascaded in two parallel paths (Fig. 3). The QCout calculation is generated based on voltage division of X and Y signals, which are connected by means of p-type and n-type CNTFET switches. Only two different CNT diameters are needed for adjusting the transition point of inverters. In this scheme, for CNTFETs with diameters of 0.783 nm and 1.487 nm, the chirality numbers would be (10, 0) and (19, 0), respectively, and accordingly the threshold voltage values ( $|V_t|$ ) would be 0.557 and 0.293 V, respectively. The relationships between chirality numbers, CNT diameter, and CNTFET threshold voltage have been given in detail by Kim et al. (2009) and Sharifi et al. (2015).

Fig. 3 The first proposed carry generation unit

The operation of the carry generation unit can be briefly described as follows:

If the inputs (QC<sub>out 1</sub> and QC<sub>out 2</sub>) become '0', the output of the first inverter in each path will be equal to logic '2' because of being driven by a  $2/3 \cdot V_{DD}$  supply. This voltage produces the required  $V_t$  to turn on the n-FET of the next inverters and this condition forces the X and Y nodes to be shorted to ground. Consequently, the output voltage of QCout also equals logic '0'. If the inputs become '1', the output voltage of the first inverter in each path will be equal to 0 V due to being driven by ground. Then, it turns on the p-FET of the next inverters, which results in the output voltage of QC<sub>out</sub> also being equal to logic '1'. Finally, if one of the inputs becomes '1' and the other becomes '0', the outputs of the inverters will be logic '2' and '0', respectively, and by a voltage division, logic '1' is produced at the output of QCout. Note that when inputs are the same, there is no static power as no ON path exists from  $V_{\rm DD}$  to ground.

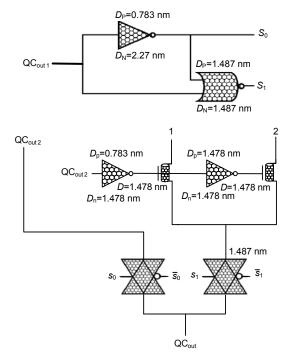

## 3.2 The second proposed carry generation unit (based on a multiplexer)

Another efficient method to design the carry generation unit is based on an efficient design of a binary two-to-one MUX. This MUX consists of a CNTFET binary decoder, transmission switches and inverters (Fig. 4). The decoder produces signals  $S_0$  and  $S_1$  as the input signals for MUX, which act as selectors in the transmission gates. Other required selector signals are generated by the CNTFET-based inverters. According to the logic of QC<sub>out</sub> (Table 1), when QC<sub>out 1</sub> is '0', the QC<sub>out signal</sub> is similar to QC<sub>out 2</sub> and consequently QC<sub>out 1</sub> can be transferred to the output. In addition, this proposed carry generator uses a simple module to generate the QC<sub>out</sub> signal when QC<sub>out 1</sub> is '1'.

This simple module is constructed based on the n-type CNTFET switches, which are controlled by the QC<sub>out 2</sub> through the inverter, acting as threshold detectors.

The design of all the modules of the proposed quaternary full adders is based mainly on transmission switches, pass transistors and threshold detectors. Designing at switch level can considerably enhance the performance and efficiency of the circuits (Wu, 1992; Wu and Prosser, 1996; Pedram and Wu, 1997).

In addition, for designing the proposed quaternary full adders, only three distinct CNT diameters are required, which enhances the manufacturability and robustness of the designs.

Fig. 4 The second proposed carry generation unit

### 4 Simulation results and comparison

In this section, the performance of the proposed quaternary full adders is examined under various conditions and is compared with those of previous designs. For this purpose, designs were simulated through a Synopsys HSPISE simulator using the 32 nm Stanford CNTFET comprehensive SPICE model including non-idealities (Deng, 2007; Deng and Wong, 2007a; 2007b). This standard model has been designed for MOSFET-like CNTFET devices, in which one or more CNTs are used in each channel of the transistor. This model also considers parasitic, inter-CNT charge screening, Schottky barrier effects at the contacts, and doped source-drain extension regions. Furthermore, the model includes a full transcapacitance network for more accurate transient and dynamic performance simulations. The important parameters of the CNTFET and their values, with brief descriptions, are shown in Table 2 (Deng and Wong, 2007a; 2007b).

This precise model is commonly used to simulate the CNTFET-based logic and arithmetic building blocks. However, to simulate larger circuits, this model will be quite time consuming and even may not

converge in a reasonable time. For larger circuits, other semiempirical SPICE models based on analytical approximations proposed by Marani and Perri (2011; 2012; 2014), Gelao *et al.* (2011), and Marani

Table 2 Some MOSFET-like CNTFET model parameters

|                                                            | •                           |

|------------------------------------------------------------|-----------------------------|

| Parameter                                                  | Value                       |

| Physical channel length                                    | 32 nm                       |

| Mean free path in the intrinsic CNT                        | 100 nm                      |

| Length of doped CNT drain-side region                      | 32 nm                       |

| Length of doped CNT source-side region                     | 32 nm                       |

| Mean free path in p <sup>+</sup> /n <sup>+</sup> doped CNT | 15 nm                       |

| Distance between the centers of two adjacent               | ≤30 nm                      |

| CNTs within the same gate                                  |                             |

| Sub-lithographic pitch                                     | 4 nm                        |

| Thickness of high-k top gate dielectric                    | 4 nm                        |

| Dielectric constant of high-k top gate dielec-             | 16                          |

| tric material (HfO <sub>2</sub> )                          |                             |

| Dielectric constant of substrate (SiO <sub>2</sub> )       | 4                           |

| Coupling cap between the channel region and                | $40 \text{ aF/}\mu\text{m}$ |

| the substrate $(SiO_2)$                                    |                             |

| Fermi level of the doped S/D CNT                           | 6 eV                        |

| Work function of S/D metal contacts                        | 4.6 eV                      |

| CNT work function                                          | 4.5 eV                      |

et al. (2013; 2014) are recommended, which considerably reduces the computational time.

The proposed CNTFET-based quaternary adders were compared with the existing quaternary full adders reviewed in Section 3. To make the comparisons fairer, all the previous circuits were redesigned and optimized in terms of energy efficiency based on the CNTFET technology.

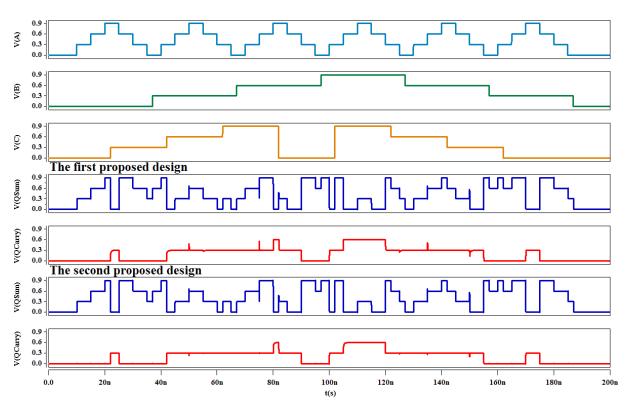

The quaternary adders were simulated at room temperature and with a 0.9 V supply voltage considering a 0.7 fF load capacitance and with quaternary input signals based on Thoidis *et al.* (1998). Fig. 5 indicates the transient responses of the proposed quaternary full adders, which confirms their correct functionality.

The simulation results, including propagation delay, average power consumption, average energy, and static power consumption of the quaternary full adders, are listed in Table 3.

The proposed designs have considerably fewer transistors than the quaternary full adder of da Silva *et al.* (2006) but have more than the designs of Asif and Vesterbacka (2012) and Sharifi *et al.* (2015).

Fig. 5 The transient response of the proposed quaternary full adders

| Dagian                                       | Delay | rowei     | Energy | Static power | Nullibel of |

|----------------------------------------------|-------|-----------|--------|--------------|-------------|

| Design                                       | (ps)  | $(\mu W)$ | (aJ)   | (µW)         | devices     |

| The first proposed QFA                       | 78.1  | 8.54      | 667    | 3.86         | 190         |

| The second proposed QFA                      | 85.9  | 7.67      | 658    | 3.51         | 200         |

| The QFA of da Silva et al. (2006)            | 193.3 | 13.70     | 2646   | 8.51         | 320         |

| The QFA based on Asif and Vesterbacka (2012) | 173.1 | 37.87     | 6557   | 22.48        | 160         |

| The QFA of Sharifi et al. (2015)             | 71.4  | 57.73     | 4125   | 41.57        | 154         |

Table 3 Performance comparison of the quaternary adders (QFAs)

However, the designs of Asif and Vesterbacka (2012) and Sharifi *et al.* (2015) are not inherently quaternary and the main part of these circuits is a binary circuit.

In addition, these circuits use radix converters which impose a considerable power consumption on the whole design, which is clearly indicated by the results. Moreover, the circuit of Sharifi *et al.* (2015) has four capacitors, which occupy a huge area compared to those of a typical CNTFET.

According to the simulation results, the proposed quaternary full adder designs have a delay comparable to that of the design of Sharifi *et al.* (2015) and significantly lower delay compared with the other designs. In addition, the proposed quaternary full adders have considerably lower average power, energy, and static power consumption than the other quaternary full adder. The higher performance of the proposed designs is due mainly to their shorter critical paths and considerably smaller number of transistors, which lead to smaller path resistance and smaller total switching capacitance.

Generally, comparing the proposed methods, the first one leads to 10 fewer transistors and lower delay. However, the second design has lower average power, energy consumption, and static power dissipation, which makes it more suitable for energy-efficient applications.

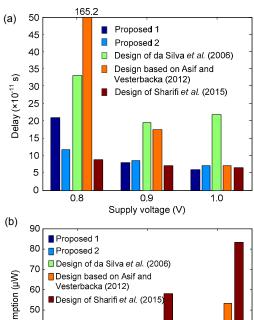

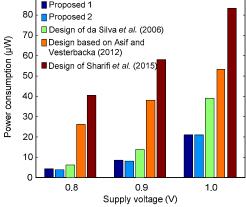

To evaluate the performance of the proposed quaternary full adders at different supply voltages, they were simulated at 0.8, 0.9, and 1 V supply voltages. Their propagation delay and average power consumption were measured (Fig. 6). Simulation results indicate the superiority of the novel proposed quaternary full adder circuits, especially in terms of power consumption, at all of these supply voltages.

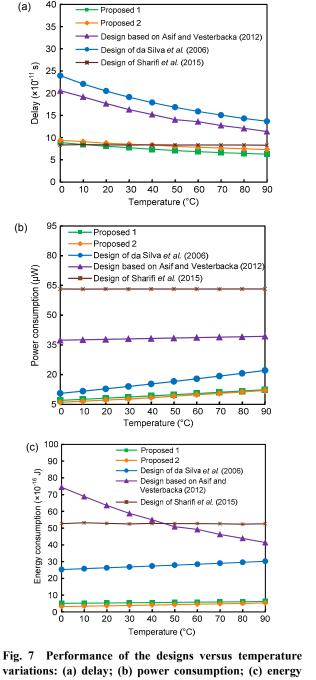

In addition, the designs were simulated at various temperatures ranging from 0 to 90 °C, at 0.9 V supply voltage, to evaluate their sensitivity to ambient

Fig. 6 Performance of the designs at different supply voltages: (a) delay; (b) power consumption

temperature variation. The results indicate little parametric variation in the proposed designs in the presence of temperature variation compared to the other quaternary full adders (Fig. 7).

As the design of the proposed CNFEET-based quaternary full adders is based on the multiple  $V_{th}$  method, the impact of process variation on the threshold voltage of the CNTFETs should definitely be considered. The most important parameters which impact the operation of a CNTFET are the diameter and density of its nanotubes.

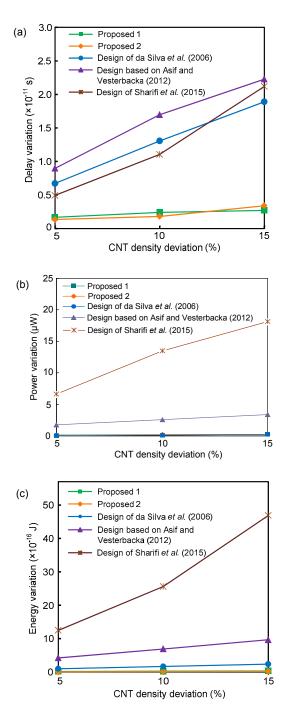

variations: (a) delay; (b) power consumption; (c) energy consumption

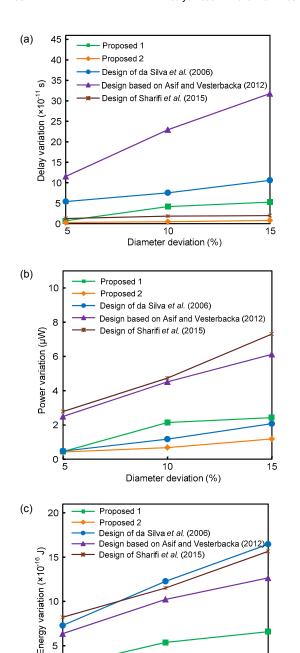

Accordingly, a Monte Carlo simulation was conducted to assess these process variations with  $\pm 5$ to  $\pm 15\%$  Gaussian distributions and variation at the  $\pm 3\sigma$  level. Figs. 8 and 9 show the variation in the performance parameters of the quaternary adders against the variation in CNT density and diameter. It can be inferred from the results that the proposed CNTFET-based quaternary full adders are considerably less sensitive to process variations compared to the other designs, due mainly to the considerably lower number of transistors and lower number of required distinct CNT diameters.

Fig. 8 Parameter variations of the designs with respect to carbon nanotube (CNT) density variation: (a) delay variation; (b) power variation; (c) energy variation

Fig. 9 Parameter variations of the designs with respect to diameter variation: (a) delay variation; (b) power variation; (c) energy variation

10 Diameter deviation (%)

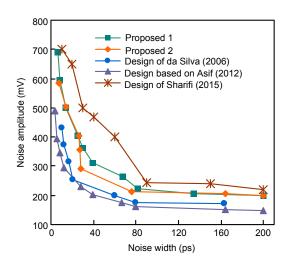

The sensitivity of the circuit to input noise becomes more critical in MVL circuits. This makes noise tolerance another important parameter for evaluating circuit performance. To measure the tolerance of the proposed circuits to input noise pulses, a noise immunity curve (NIC) was used. This curve is formed by the loci of input noise pulses with amplitude ( $V_{\text{noise}}$ ) and width ( $T_{\text{noise}}$ ) that appear at the inputs of circuits and cause the circuit to have a logic error. All points above the curve for a particular width represent noise pulses that cause output errors. Thus, a digital circuit with a higher NIC has more noise immunity. A tunable noise generation circuit described in detail by Balamurugan and Shanbhag (2001) was used to obtain the NIC. The NIC results for all the quaternary full adder cells are shown in Fig. 10. According to the results, the proposed designs have higher noise immunity than other quaternary designs, except the design of Sharifi et al. (2015) in which the output stage has a capacitive network which enhances the noise immunity but increases its power consumption and area wastage.

Fig. 10 Noise immunity curves for the proposed quaternary full adders

#### 5 Conclusions

In this paper, two new CNTFET based quaternary full adder cells are proposed. Using the outstanding properties of CNTFETs makes the design of MVL circuits easier and efficient compared to using MOSFETs. The presented circuits were examined using a HSPICE simulator with a 32 nm CNTFET model. The results of the simulations conducted under various conditions indicate that the proposed circuits are faster, consume less power, and consequently have a lower energy consumption than the

state-of-the-art quaternary full adders. In addition, the circuits were precisely analyzed in terms of robustness against process, voltage, and temperature variation and noise, and the results confirm the higher robustness of the proposed designs.

#### References

- Asif, S., Vesterbacka, M., 2012. Performance analysis of radix-4 adders. *Integr. VLSI J.*, **45**(2):111-120. http://dx.doi.org/10.1016/j.vlsi.2011.09.004

- Balamurugan, G., Shanbhag, N.R., 2001. The twin-transistor noise-tolerant dynamic circuit technique. *IEEE J. Sol.-State Circ.*, **36**(2):273-280. http://dx.doi.org/10.1109/4.902768

- Chen, Y., Wang, B., Poa, P.C.H., *et al.*, 2007. (*n*, *m*) selectivity of single-walled carbon nanotubes by different carbon precursors on Co-Mo catalysts. *J. Am. Chem. Soc.*, **129**(29):9014-9019. http://dx.doi.org/10.1021/ja070808k

- da Silva, R.C.G., Boudinov, H.I., Carro, L., 2006. A low power high performance CMOS voltage-mode quaternary full adder. IFIP Int. Conf. on Very Large Scale Integration, p.1130-1133.

http://dx.doi.org/10.1109/VLSISOC.2006.313231

- Datla, R., 2009. Design and Validation of Quaternary Arithmetic Circuits. PhD Thesis, Southern Methodist University, USA.

- Datla, S.R., Thornton, M.A., Hendrix, L., *et al.*, 2009. Quaternary Addition Circuits Based on SUSLOC Voltage-Mode Cells and Modeling with System Verilog©. 39th IEEE Int. Symp. on Multiple-Valued Logic, p.256-261. http://dx.doi.org/10.1109/ISMVL.2009.66

- Deng, J., 2007. Device Modeling and Circuit Performance Evaluation for Nanoscale Devices: Silicon Technology Beyond 45 nm Node and Carbon Nanotube Field Effect Transistors. PhD Thesis, Stanford University, USA.

- Deng, J., Wong, H.S.P., 2007a. A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: model of the intrinsic channel region. *IEEE Trans. Electron Dev.*, 54(12): 3186-3194. http://dx.doi.org/10.1109/TED.2007.909030

- Deng, J., Wong, H.S.P., 2007b. A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application—Part II: full device model and circuit performance benchmarking. *IEEE Trans. Electron Dev.*, **54**(12):3195-3205. http://dx.doi.org/10.1109/TED.2007.909043

- Dubrova, E., 1999. Multiple-valued logic in VLSI: challenges and opportunities. Proc. NORCHIP Conf., p.340-350.

- Gelao, G., Marani, R., Diana, R., *et al.*, 2011. Semi-empirical SPICE model for n-type conventional CNTFETs. *IEEE Trans. Nanotechnol.*, **10**(3):506-512. http://dx.doi.org/10.1109/TNANO.2010.2049499

- Hurst, S.L., 1984. Multiple-valued logic—its status and its future. *IEEE Trans. Comput.*, **33**(12):1160-1179. http://dx.doi.org/10.1109/TC.1984.1676392

- Kim, Y.B., Kim, Y.B., Lombardi, F., 2009. Novel design methodology to optimize the speed and power of the CNTFET circuits. 52nd IEEE Int. Midwest Symp. on Circuits and Systems, p.1130-1133. http://dx.doi.org/10.1109/MWSCAS.2009.5235967

- Liang, J., Chen, L., Han, J., et al., 2014. Design and evaluation of multiple valued logic gates using pseudo N-type carbon nanotube FETs. *IEEE Trans. Nanotechnol.*, **13**(4): 695-708.

http://dx.doi.org/10.1109/TNANO.2014.2316000

- Lin, A., Patil, N., Ryu, K., *et al.*, 2009. Threshold voltage and on–off ratio tuning for multiple-tube carbon nanotube FETs. *IEEE Trans. Nanotechnol.*, **8**(1):4-9. http://dx.doi.org/10.1109/TNANO.2008.2004706

- Lin, S., Kim, Y.B., Lombardi, F., 2011. CNTFET-based design of ternary logic gates and arithmetic circuits. *IEEE Trans. Nanotechnol.*, **10**(2):217-225. http://dx.doi.org/10.1109/TNANO.2009.2036845

- Mansoori, G.A., Soelaiman, T.F., 2005. Nanotechnology—an introduction for the standards. *J. ASTM Int.*, **2**(6):1-21. http://dx.doi.org/10.1520/JAI13110

- Marani, R., Perri, A.G., 2011. A compact, semi-empirical model of carbon nanotube field effect transistors oriented to simulation software. *Current Nanosci.*, 7(2):245-253. http://dx.doi.org/10.2174/157341311794653613

- Marani, R., Perri, A.G., 2012. A DC model of carbon nanotube field effect transistor for CAD applications. *Int. J. Electron.*, **99**(3):427-444. http://dx.doi.org/10.1080/00207217.2011.629223

- Marani, R., Perri, A.G., 2014. Modelling of CNTFETs for computer aided design of A/D electronic circuits. *Current Nanosci.*, 10(3):326-333. http://dx.doi.org/10.2174/15734137113096660124

- Marani, R., Gelao, G., Perri, A.G., 2013. Modelling of carbon nanotube field effect transistors oriented to SPICE software for A/D circuit design. *Microelectron. J.*, **44**(1):33-39. http://dx.doi.org/10.1016/j.mejo.2011.07.012

- Marani, R., Gelao, G., Perri, A.G., 2014. Comparison of ABM SPICE library with Verilog-A for compact CNTFET model implementation. *Current Nanosci.*, **8**(4):556-565. http://dx.doi.org/10.2174/157341312801784230

- Moaiyeri, M.H., Doostaregan, A., Navi, K., 2011. Design of energy-efficient and robust ternary circuits for nanotechnology. *IET Circ. Dev. Syst.*, 5(4):285-296. http://dx.doi.org/10.1049/iet-cds.2010.0340

- Moaiyeri, M.H., Navi, K., Hashemipour, O., 2012. Design and evaluation of CNFET-based quaternary circuits. *Circ. Syst. Signal Process.*, **31**(5):1631-1652. http://dx.doi.org/10.1007/s00034-012-9413-2

- Navi, K., Doostaregan, A., Moaiyeri, M.H., et al., 2011. A hardware-friendly arithmetic method and efficient implementations for designing digital fuzzy adders. Fuzzy Sets Syst., 185(1):111-124. http://dx.doi.org/10.1016/j.fss.2011.06.006

- Patel, V., Gurumurthy, K.S., 2010. Arithmetic operations in multi-valued logic. *Int. J. VLSI Des. Commun. Syst.*, 1(1):21-32.

- Pedram, M., Wu, X., 1997. A new description of MOS circuits at switch-level with applications. *IEICE Trans. Fundam. Electron. Commun. Comput. Sci.*, **80**(10):1892-1901.

- Raychowdhury, A., Roy, K., 2005. Carbon-nanotube-based voltage-mode multiple-valued logic design. *IEEE Trans. Nanotechnol.*, **4**(2):168-179. http://dx.doi.org/10.1109/TNANO.2004.842068

- Raychowdhury, A., Roy, K., 2007. Carbon nanotube electronics: design of high-performance and low-power digital circuits. *IEEE Trans. Circ. Systems I*, **54**(11):2391-2401. http://dx.doi.org/10.1109/TCSI.2007.907799

- Sharifi, F., Moaiyeri, M.H., Navi, K., *et al.*, 2015. Quaternary full adder cells based on carbon nanotube FETs. *J. Comput. Electron.*, **14**(3):762-772. http://dx.doi.org/10.1007/s10825-015-0714-0

- Thoidis, I., Soudris, D., Karafyllidis, I., *et al.*, 1998. Quaternary voltage-mode CMOS circuits for multiple-valued logic. *IEE Proc.-Circ. Dev. Syst.*, **145**(2):71-77. http://dx.doi.org/10.1049/ip-cds:19981763

- Wu, X., 1992. Theory of transmission switches and its application to design of CMOS digital circuits. *Int. J. Circ. Theory Appl.*, **20**(4):349-356. http://dx.doi.org/10.1002/cta.4490200402

- Wu, X., Prosser, F., 1996. Design theory of digital circuits at switch level. *Sci. China Technol. Sci.*, **39**(4):424-434.

- Yang, F., Wang, X., Zhang, D., et al., 2014. Chirality-specific growth of single-walled carbon nanotubes on solid alloy catalysts. *Nature*, **510**(7506):522-524. http://dx.doi.org/10.1038/nature13434